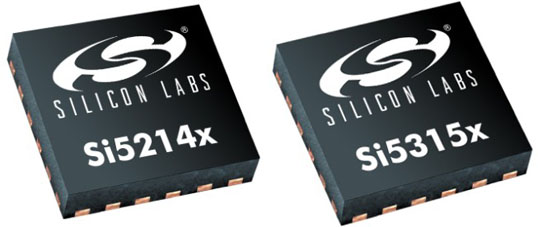

高性能模擬與混合信號IC領導廠商Silicon Laboratories (芯科實驗室有限公司)今日宣布擴展其PCI Express(PCIe)時鐘發生器和時鐘緩沖器產品組合,為業界提供范圍最廣的時鐘解決方案,以滿足PCIe Gen 1/2/3標準的嚴格要求。Silicon Labs擴展的PCIe定時產品組合包括現用Si5214x時鐘發生器和Si5315x時鐘緩沖器,此兩款產品針對功耗和成本敏感型PCIe應用;同時還包括針對FPGA和SoC設計應用的Si5335網絡定制時鐘發生器/緩沖器,這些設計要求支持多種差分時鐘格式,同時還需符合PCIe標準。

PCIe互連標準已被大量應用廣泛采用,包括:消費類電子產品、刀片服務器、存儲、嵌入式計算、IP網關和工業系統。PCIe接口也可用于FPGA和SoC裝置,為設計者提供靈活和高性能系統內數據傳輸解決方案。Silicon Labs公司利用其專利混合信號技術為PCIe設計提供一套靈活的時鐘解決方案,可滿足不同市場和應用需求。

Silicon Labs公司定時產品總經理Mike Petrowski表示:"通過把'一站式采購'定時IC供應模式帶給PCIe市場控制工程網版權所有,我們能為客戶提供最大靈活性,使客戶根據其PCIe應用需求選擇最佳時鐘解決方案,我們擴展的PCIe 定時解決方案組合是開發人員現用時鐘選項的完整補充,包括最小化功耗、增強信號集成度和降低成本,同時也為基于FPGA設計提供業內高度定制化的時鐘發生器和緩沖器。"

現用PCIe時鐘解決方案

Si5214x時鐘發生器和Si5315x時鐘緩沖器產品系列有2-9路的時鐘輸出,提供業界最高性能。新型PCIe時鐘發生器和緩沖器的電源效率為其他時鐘方案的兩倍,更低功耗有助于減少散熱、減少額外冷卻組件和電源穩壓器的需要;同時此芯片滿足PCIe對抖動性能最大50%容差的要求控制工程網版權所有,帶來更好系統穩定性和降低誤碼率。

為進一步簡化設計復雜性,Si5214x和Si5315x產品利用輸出緩沖技術來集成所有外部終端電阻,從而減少組件數量、BOM成本、板面積和功耗。作為市場上最小PCIe時鐘裝置,新型時鐘發生器和緩沖器是空間受限型應用的理想選擇。

為克服電磁干擾(EMI)和射頻干擾(RFI),Si5214x 和Si5315x產品系列每個獨立輸出均具有可編程邊沿速率和失真控制。使用內置I2C接口,開發人員無需更多組件即可微調信號并修復運行中的完整性問題。此信號完整性調節能力使產品更符合對EMI的要求,縮短PCIe電路板設計上市時間。

網絡定制4路時鐘發生器/緩沖器

Si5335時鐘發生器/緩沖器IC是業界最容易定制的時鐘解決方案CONTROL ENGINEERING China版權所有,特別針對PCIe和基于FPGA應用所面臨的定時挑戰。通過Silicon Labs公司網站www.silabs.com/Clockbuilder易于使用的ClockBuilder™ Web配置實用工具,客戶可以在2周內獲得工廠定制化、引腳控制的Si5335器件(沒有最小訂單限制),Si5335輸出可配置多達四個輸出頻率,范圍為1-350 MHz任意組合。單一零件型號可以最多指定3個唯一的器件配置,因此Si5335可以代替3個獨立時鐘發生器或緩沖器,從而允許開發人員在多個設計中重復使用定制Si5335器件。

Si5335時鐘發生器/緩沖器IC可提供高達5個用戶可分配控制引腳,以簡化PCIe和基于FPGA的系統設計,并使用PCIe兼容的擴頻時鐘選項來簡化EMI兼容性。 Si5335器件采用Silicon Labs專利MultiSynth小數分頻技術,使其在每個輸出時鐘上的任意頻率合成均具有亞皮秒級抖動性能。Si5335性能超越PCIe、以太網和海量存儲行業標準的性能要求,其最大抖動為0.45ps(rms),優于PCIe 3.0抖動性能要求(1ps)兩倍多。

Si5335通過支持任意差分格式組合,例如LVPECL、LVDS、CML和單端格式(比如LVCMOS),簡化多芯片時鐘面臨的挑戰www.cechina.cn,并減少時鐘發生器和緩沖器數量,芯片支持4個差分輸出或多達8個LVCMOS輸出的任意組合。輸出格式的靈活性使設計人員容易適應PCIe、FPGA和SoC嵌入式應用中常見的對多種輸出信號格式和電源電壓的要求。

價格和供貨

Silicon Labs公司最新PCIe時鐘發生器和緩沖器IC現已開始供貨,支持多種小尺寸封裝。對于一萬顆采購量,Si5214x時鐘發生器單價為0.96美元起;Si5315x時鐘緩沖器單價為0.94美元起;200MHz輸出配置的Si5335時鐘發生器/緩沖器單價為3.01美元起。

Silicon Labs公司還提供評估平臺CONTROL ENGINEERING China版權所有,加速PCIe應用開發。 Si52144-EVB 4路輸出時鐘發生器評估板、Si52154-EVB 4路輸出時鐘緩沖器評估板和Si5338-EVB時鐘發生器/緩沖器評估板(安裝最新的ClockBuilder桌面軟件可用于對Si5335進行評估),單個售價為125美元。 Si52147-EVB 9路輸出時鐘發生器評估板和Si52159-EVB 9路輸出時鐘緩沖評估板,單個售價為175美元。

更多有關Silicon Labs公司PCIe時鐘發生器和緩沖器產品組合信息或訂購樣品和開發板,請瀏覽網站:www.silabs.com/pci-express-clocks